Сумматоры и субтракторы

арифметические устройства.

Сумматоры и субтракторы

Основной элементарной операцией, выполняемой над кодами чисел в цифровых устройствах, является арифметическое сложение.

Сумматор – электронная логическая схема, выполняющая арифметическое сложение кодов двух чисел. Этот узел лежит в основе арифметико-логического устройства ЭВМ (АЛУ).

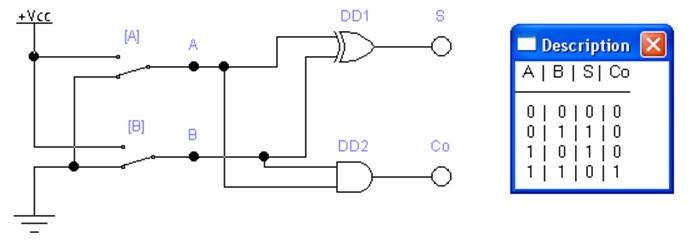

Полусумматор. Простейшего устройства, являющегося звеном сумматора. Это устройство реализует сложение двух одноразрядных двоичных чисел А и В. В результате получается двухразрядное двоичное число. Его младшую цифру обозначим S (от лат. Summa), а старшую, которая будет перенесена в старший разряд, – Co (от англ. Carry out – выходной перенос).

|

Слагаемые |

Перенос |

Сумма |

|

|

A |

B |

Co |

S |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

0 |

Полусумматор имеет два входа (слагаемые) и два выхода – сумму в данном разряде и перенос в следующий разряд. Из таблицы видно, что перенос формируется ЛФ AND (И): Co = A & B.

Для составления ЛФ для S можно обратиться к логическому конвертеру, но здесь результат очевиден – функция Исключающее ИЛИ (XOR – от eXclusive OR). Исключающее ИЛИ осуществляет математическую операцию сложение двух бит по модулю 2. Математики обозначают эту операцию знаком «псевдоплюс».

Рис. 1. Схема полусумматора на ЛЭ XOR и AND

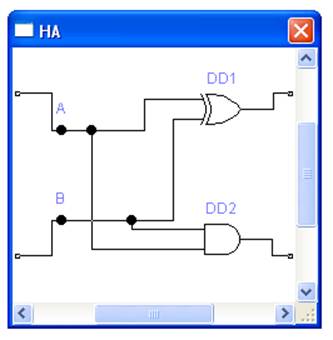

В программе EWB имеется специальный инструментарий для выделения функциональных блоков из больших схем. Его можно использовать для создания дополнительной библиотеки цифровых узлов.

Проведем построение субблока полусумматора по схеме рис. 1. Путем растяжения выделенных частей, придадим схеме такой вид, чтобы внутрь выделяющей рамки входил только полусумматор. Это и будет субблок (подсхема). Проводники, пересекающие контур субблока, образуют его выводы, поэтому их число и расположение надо контролировать.

После выделения субблока, пока его элементы имеют активный красный цвет, входим в меню Circuit (цепь) и выбираем Create Subcircuit. В появившемся меню Subcircuit впечатываем в строке Name название, например НА (Half—Adder), и выбираем Сору from Circuit. На рабочем поле появится дополнительное окно с развернутой схемой субблока (рис. 2).

Рис 2. Создание субблока полусумматора

Эту подсхему можно отредактировать стандартными приемами. Можно добавить выводы, вытянув провод из нужной точки до края внутреннего поля окна (возникнет дополнительная контактная площадка). Если контактную площадку вытянуть за пределы окна, то соответствующий вывод будет удален. После редактирования и проверки правильности подсхемы это окно можно закрыть.

Для выбора схемного изображения субблока в свернутом виде, надо нажать в ряду выбора компонентов на иконку Favorites (Избранные). В результате получим иконку с изображением субблоков и возможность дальнейшего выбора Choose SUB. Выбрав в последнем окне Accept (согласиться), получим искомое схемное изображение субблока в свернутом виде. К внутреннему содержанию субблока можно вернуться двойным щелчком по его схемному изображению.

Библиотеку раздела Favorites можно докомплектовать уже существующими и часто используемыми компонентами, нажав на соответствующую иконку ПКМи выбрав опцию Add to favorites (Добавить к избранным). Создание такой специализированной пользовательской панели для конкретной схемы иногда бывает удобно. Для использования полученного субблока в новом окне, необходимо скопировать схемное изображение субблока в свернутом виде в буфер обмена.

Открыв новое окно (New) и нажав на иконку Favorites, увидим, что внутри нет никаких элементов. После команды Past на экране возникнет схемное изображение субблока, а в открытом окне – Favorites иконка для его выбора.

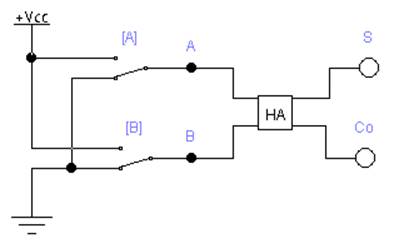

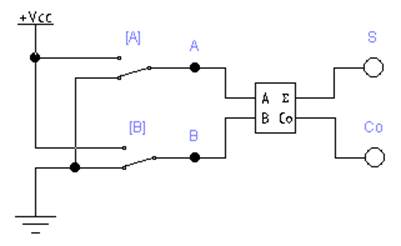

В цифровом наборе Digital программы EWB существует специальный библиотечный компонент полусумматор (англ. – Half-Adder). Он эквивалентен созданному нами субблоку, но имеет иное графическое оформление. Данный схемный компонент располагается в основной библиотеке, что удобнее.

Пример создания субблока приведен по двум соображениям:

· показать технику создания новых субблоков;

· раскрыть возможное содержание библиотечного полусумматора.

В отличие от вновь созданных субблоков готовые библиотечные компоненты не раскрывают своих схем и не дают возможности их редактировать (в большинстве компонентов редактируются только их параметры).

Схемы, в которых использован вновь созданный и стандартный полусумматоры показаны на рис. 3 и 4.

Рис. 3. Схема включения разработанного полусумматора

Рис. 4. Схема включения библиотечного полусумматора

Данная схема называется полусумматором, так как реализует суммирование одноразрядных двоичных чисел без учета переноса из младшего разряда.

Полный одноразрядный сумматор. При сложении старших разрядов многоразрядных двоичных слов необходимо в схеме учесть перенос из предыдущего (младшего) разряда. Такое устройство является полным сумматором. Оно должно иметь три входа: А и В – одноименные разряды двух складываемых чисел, Сi – входной перенос из предыдущего (младшего) разряда (от англ. Carry in – входной перенос) и два выхода: S – сумма в данном разряде и Co – перенос в следующий (старший) разряд.

Таблица истинности для одноразрядного сумматора:

|

Входы |

Выходы |

|||

|

A – первое слагаемое |

B – второе слагаемое |

Ci – перенос |

S – сумма |

Co – перенос |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

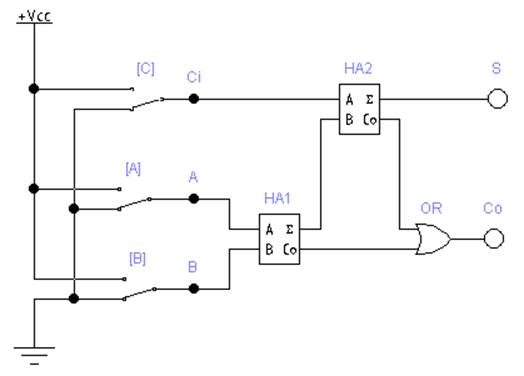

Сумматор удобно представить в виде двух полусумматоров, из которых первый суммирует разряды А и В, а второй к результату прибавляет бит переноса Ci (рис. 5).

Рис. 5. Схема сумматора на двух полусумматорах

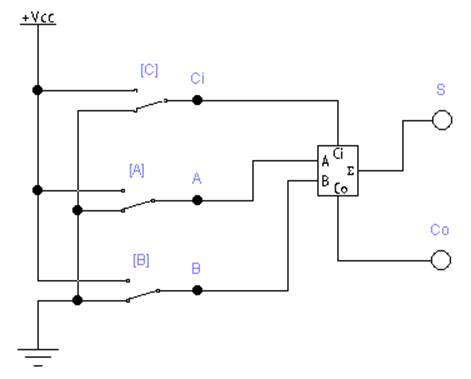

В цифровом наборе Digital программы EWB существует специальный библиотечный компонент полный сумматор (англ. – Full-Adder) (рис. 6).

Рис. 6. Схема включения библиотечного сумматора

Многоразрядный сумматор – устройство, предназначенное для сложения двух многоразрядных кодов, формирующее на выходе код суммы и сигнал переноса в случае, если результат сложения не может быть представлен кодом, разрядность которого совпадает с разрядностью кодов слагаемых.

Многоразрядные сумматоры подразделяются на:

· последовательные – операция сложения выполняется последовательно разряд за разрядом, начиная с младшего;

· параллельные – все разряды входных кодов суммируются одновременно.

Различают также:

· комбинационные сумматоры – не имеют собственной памяти;

· накапливающие сумматоры – снабжены собственной внутренней памятью, в которой аккумулируются результаты выполненной операции (каждое слагаемое прибавляется к уже имеющемуся в устройстве значению).

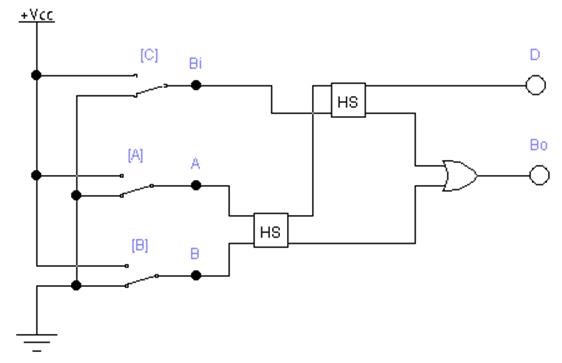

Параллельный сумматор с последовательным переносом – строится как цепочка полных одноразрядных сумматоров, соединенных последовательно по цепям переноса. На каждый разряд ставится одноразрядный сумматор, причем выход (перенос) сумматора младшего разряда подключен ко входу сумматора старшего разряда. Для суммирования младших разрядов чисел полусумматора уже достаточно, так как в этом случае отсутствует сигнал входного переноса.

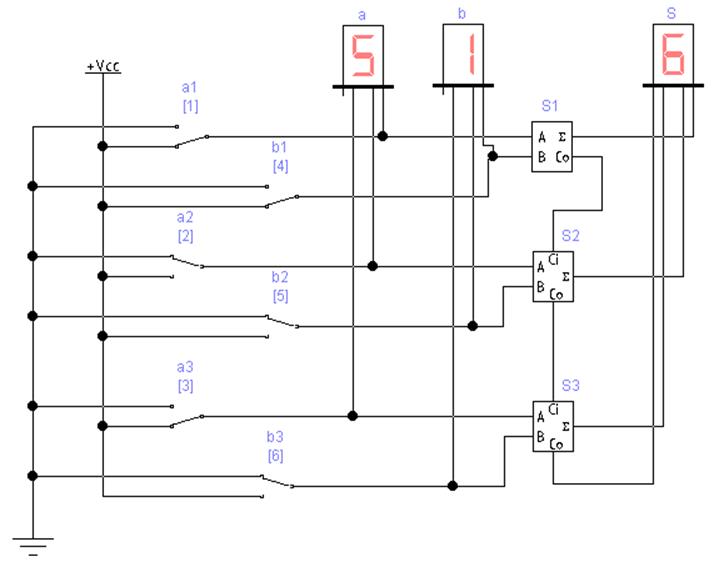

На рис. 7 представлена схема суммирования двух трехразрядных двоичных чисел А + B = S . В поразрядной записи операция имеет следующие обозначения:

(а3 а2 а1)+(b3 b2 b1)=(s4 s3 s2 s1)

Рис. 7. Схема суммирования трехразрядных чисел

В соответствии с изложенным, соберем схему 3-разрядного параллельного сумматора с последовательным переносом (рис. 10).

Рис. 10. Схема 3-разрядного параллельного сумматора

с последовательным переносом

Субтракторы (вычитатели) выполняют операции, противоположные тем, которые выполняют сумматоры.

|

Операнды |

Заем |

Разность |

|

|

A |

B |

Bo |

D |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

0 |

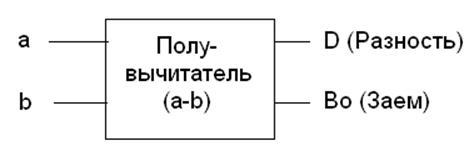

Полувычитатель имеет два входа (уменьшаемое и вычитаемое) и два выхода – разность в данном разряде и заем из старшего разряда.

Рис. 11. Общая схема полувычитателя

Рис. 12. Схема полувычитателя на ЛЭ XOR, NOT и AND

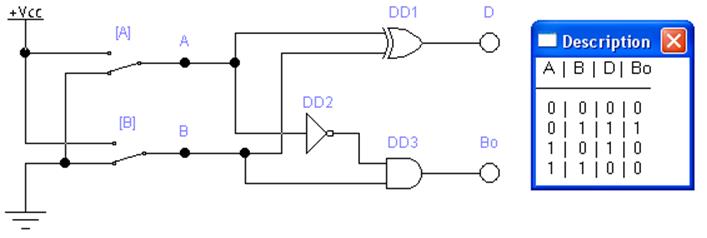

Полный вычитатель (рис. 13) имеет входы a, b, Bi и выходы D, Bo. По аналогии с полным сумматором полный вычитатель можно собрать из двух полувычитателейи логического элемента ИЛИ (рис. 14).

Рис. 13. Общая схема полного вычитателя

Таблица истинности для одноразрядного вычитателя:

|

Входы |

Выходы |

|||

|

A – уменьшаемое |

B – вычитаемое |

Bi – перенос |

D – разность |

Bo – перенос |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

1 |

Рис. 14. Схема полного вычитателя на двух полувычитателях

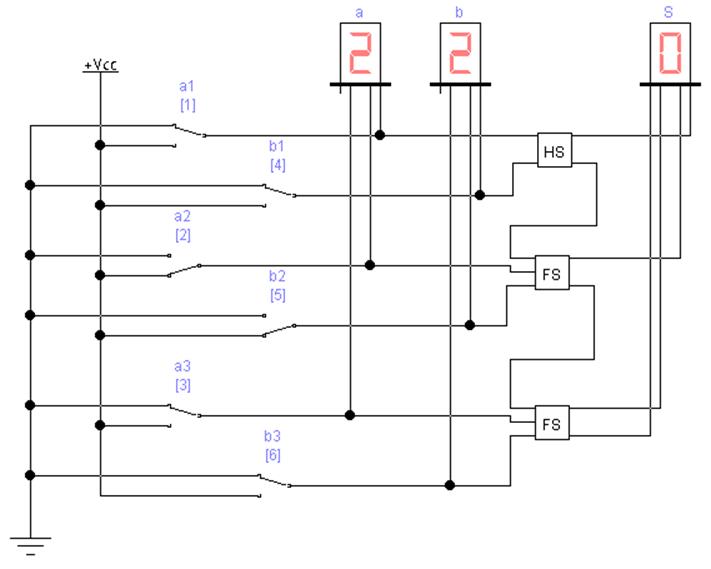

В соответствии с изложенным, соберем схему 3-разрядного параллельного вычитателя с последовательным переносом (рис. 15).

Рис. 15. Схема 3-разрядного параллельного вычитателя

с последовательным переносом